L’électronique programmable joue un rôle central dans les innovations modernes, permettant d’ajuster dynamiquement les fonctionnalités des circuits en fonction des besoins spécifiques. Contrairement aux idées reçues, les microprocesseurs et microcontrôleurs, bien qu’ils puissent exécuter des programmes, ne sont pas considérés comme des composants programmables dans ce contexte. En réalité, cette catégorie regroupe des dispositifs comme les FPGA (Field Programmable Gate Arrays) et les CPLD (Complex Programmable Logic Devices), capables de modifier leur comportement matériel après fabrication. Par exemple, un FPGA peut contenir plus de 2 millions de portes logiques et fonctionner à des fréquences dépassant 500 MHz, offrant une flexibilité inégalée pour le prototypage rapide et les mises à jour fonctionnelles. Cette adaptabilité réduit les coûts de production de 20 à 40 % par rapport aux circuits spécifiques, accélérant le développement de systèmes électroniques avancés.

1. Définition et principes fondamentaux

Les composants programmables sont des dispositifs logiques dont le fonctionnement peut être modifié logiciellement, sans avoir à les remplacer physiquement. Les Field Programmable Gate Arrays (FPGA) et les Complex Programmable Logic Devices (CPLD) sont les deux principales familles de composants programmables. Ces dispositifs se distinguent par leur architecture et leur capacité à traiter des tâches complexes efficacement.

Un FPGA, par exemple, peut contenir plus de 2 millions de portes logiques, offrant ainsi une capacité de traitement considérable. En revanche, un CPLD dispose d’une architecture plus rigide avec un nombre plus limité de portes, souvent autour de 10 000 à 100 000. Ces différences influencent directement les performances et le choix du composant en fonction de l’application visée.

2. Composants programmables vs. microprocesseurs

Bien que les microprocesseurs et microcontrôleurs puissent exécuter des programmes, ils ne sont pas considérés comme des composants programmables dans le sens strict. Les microprocesseurs sont des unités séquentielles qui exécutent des instructions les unes après les autres, avec une fréquence d’horloge typique de 1 à 5 GHz pour les processeurs modernes. En revanche, les FPGA et CPLD sont conçus pour effectuer des opérations en parallèle, rendant possible le traitement simultané de multiples flux de données.

Cette capacité parallèle des FPGA permet d’atteindre des performances bien supérieures dans des tâches spécifiques, avec des débits allant jusqu’à 100 Gbps dans des applications de télécommunications, là où un microprocesseur aurait besoin de plusieurs cycles pour accomplir le même travail.

3. Architecture des FPGA et CPLD : une comparaison technique

3.1. FPGA : Flexibilité maximale

Les FPGA se composent de trois parties essentielles :

- Éléments logiques sous forme de Look-Up Tables (LUT) capables de gérer des fonctions logiques complexes.

- Matrices d’interconnexion pour relier les éléments logiques entre eux.

- Buffers d’entrée/sortie pour l’interaction avec les autres composants.

Un exemple représentatif est le Stratix 10 d’Intel, qui intègre 5,5 millions d’éléments logiques et peut fonctionner à des fréquences dépassant 500 MHz. Cette architecture modulaire permet aux FPGA d’être reprogrammés en fonction des besoins, garantissant une souplesse d’utilisation remarquable.

3.2. CPLD : Simplicité et efficacité

Les CPLD, quant à eux, se distinguent par une architecture plus rigide mais plus prévisible, avec des délais de propagation garantis. Un CPLD typique comme le MAX 10 d’Intel peut contenir jusqu’à 50 000 portes logiques avec une fréquence garantie pouvant atteindre 300 MHz. Leur simplicité les rend idéaux pour des applications nécessitant des temps de réponse rapides mais avec une logique moins complexe.

4. Les enjeux de la consommation énergétique

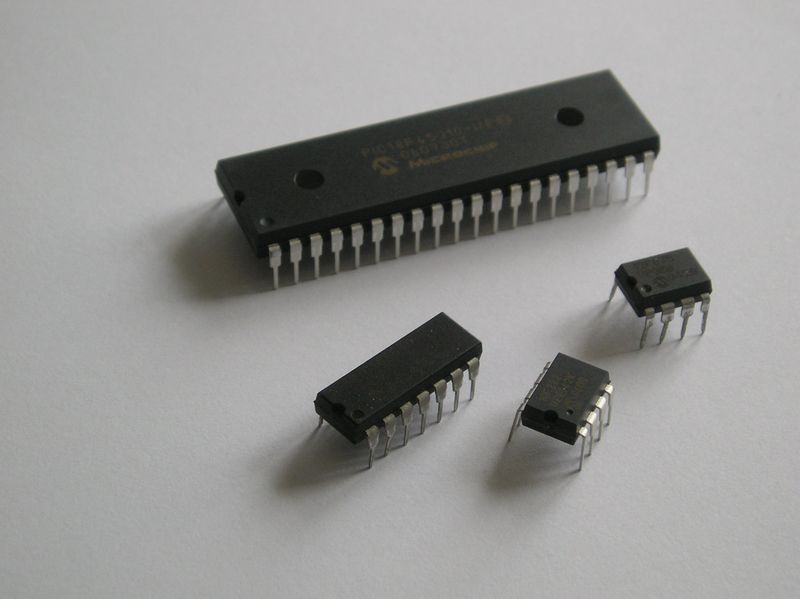

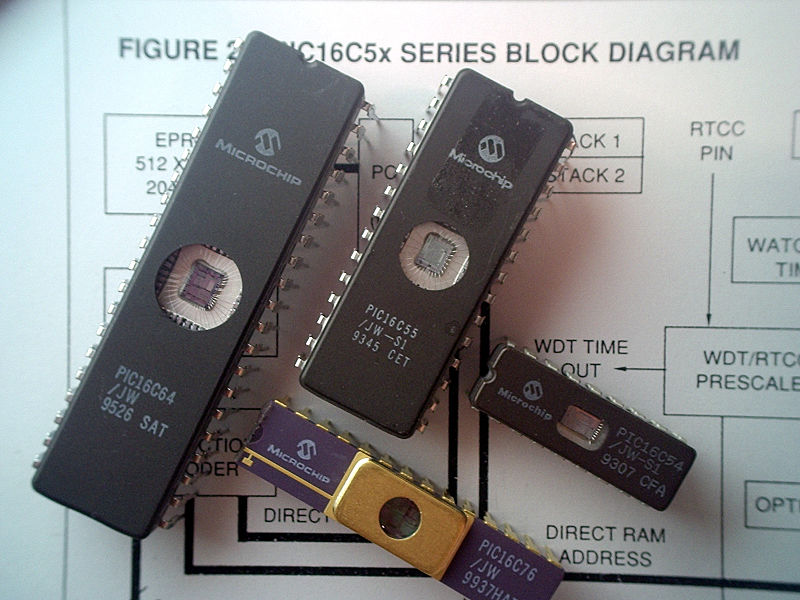

Les composants programmables offrent des performances élevées mais au prix d’une consommation énergétique importante. Par exemple, un Stratix EP1S25 peut consommer jusqu’à 6W, contre 0,05W pour un microcontrôleur PIC18F. Cette différence s’explique par le nombre élevé de portes logiques et la nécessité d’alimenter en permanence les matrices d’interconnexion.

La consommation peut devenir un facteur limitant dans des applications embarquées où l’efficacité énergétique est cruciale. Des solutions comme l’optimisation du placement/routage et l’usage de sources d’alimentation ajustables sont couramment employées pour réduire cet impact.

5. Processus de programmation des FPGA et CPLD

La programmation d’un composant programmable suit un processus structuré comprenant :

- Génération des listes de circuits à partir de langages de description matériels comme VHDL ou Verilog.

- Placement/routage, qui détermine l’emplacement des portes logiques et leurs interconnexions.

- Recherche du chemin critique (pour les FPGA uniquement), déterminant la fréquence maximale possible.

- Assemblage et programmation par transfert du code binaire dans une mémoire flash.

Ce processus peut prendre de 1 à 5 minutes pour un composant simple, mais dépasser 30 minutes pour les FPGA complexes. La complexité du placement/routage, un problème NP-complet, nécessite des algorithmes avancés et des outils logiciels spécialisés comme Quartus ou Vivado.

6. Avantages et limitations des composants programmables

6.1. Avantages

- Souplesse d’utilisation : Un même FPGA peut être reprogrammé des milliers de fois, réduisant les coûts de développement.

- Performances élevées : Les FPGA peuvent traiter des débits de plus de 400 Gbps dans les réseaux modernes.

- Coûts réduits : Grâce à une production en série, les prix des FPGA se situent entre 30 et 300 USD selon la complexité.

6.2. Limitations

- Consommation énergétique importante, nécessitant des systèmes de refroidissement adaptés.

- Complexité de développement, avec des temps de synthèse souvent longs et un débogage complexe.

- Coût humain élevé en raison de la spécialisation nécessaire des ingénieurs en électronique programmable.

7. Applications et perspectives futures

Les composants programmables sont omniprésents dans les domaines des télécommunications, de l’aéronautique et des systèmes embarqués. Par exemple, les FPGA sont utilisés dans les stations de base 5G pour le traitement en temps réel des signaux avec des latences inférieures à 1 ms.

Les perspectives d’avenir passent par l’intégration d’IA dans les FPGA et l’optimisation de la consommation énergétique. Des avancées comme les FPGAs à faible puissance (moins de 2W) devraient permettre d’élargir encore plus leur utilisation dans les appareils portables et les systèmes IoT.

Conclusion

L’électronique programmable constitue l’épine dorsale des systèmes modernes nécessitant flexibilité et performances élevées. Si les défis restent nombreux, en particulier en matière de consommation énergétique et de complexité de développement, les avantages offerts par les FPGA et CPLD en termes de personnalisation et de puissance de calcul sont indéniables. Avec des avancées continues dans les technologies de fabrication et d’optimisation logicielle, l’avenir des composants programmables semble plus prometteur que jamais, affirmant leur place comme piliers de l’innovation technologique.

Images source : Wikipedia.org – Creative Commons