Le CMOS (Complementary Metal-Oxide-Semiconductor) est une technologie clé dans la conception des circuits intégrés, représentant plus de 85 % des semi-conducteurs produits aujourd’hui. Elle est largement utilisée dans les microprocesseurs, où elle permet de réduire la consommation d’énergie, essentielle pour les processeurs modernes dépassant les 5 GHz. En mémoire, la technologie CMOS est dominante dans la fabrication des SRAM et DRAM, utilisées dans les ordinateurs et les smartphones. Dans les capteurs d’images, notamment les capteurs CMOS des caméras numériques, elle offre des résolutions dépassant 100 mégapixels, tout en consommant environ 100 fois moins d’énergie que les capteurs CCD traditionnels. Son efficacité énergétique est due à une consommation de courant quasi nulle en régime statique, avec des courants de fuite limités à quelques nanoampères. Grâce à la miniaturisation, les transistors CMOS atteignent aujourd’hui des dimensions inférieures à 3 nm, permettant une densité d’intégration de plusieurs milliards de transistors par puce. Cette technologie continue d’évoluer pour répondre aux besoins croissants en performance et en efficacité énergétique.

Principes de fonctionnement

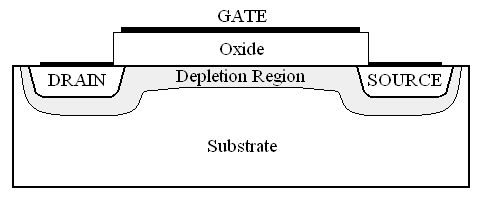

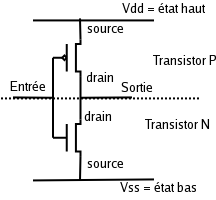

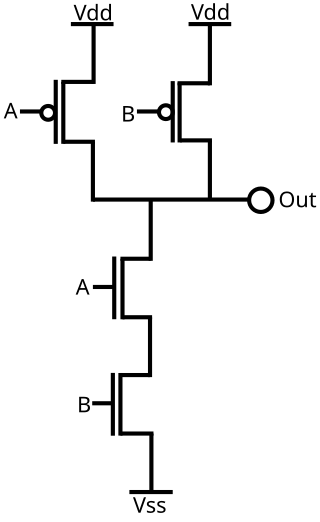

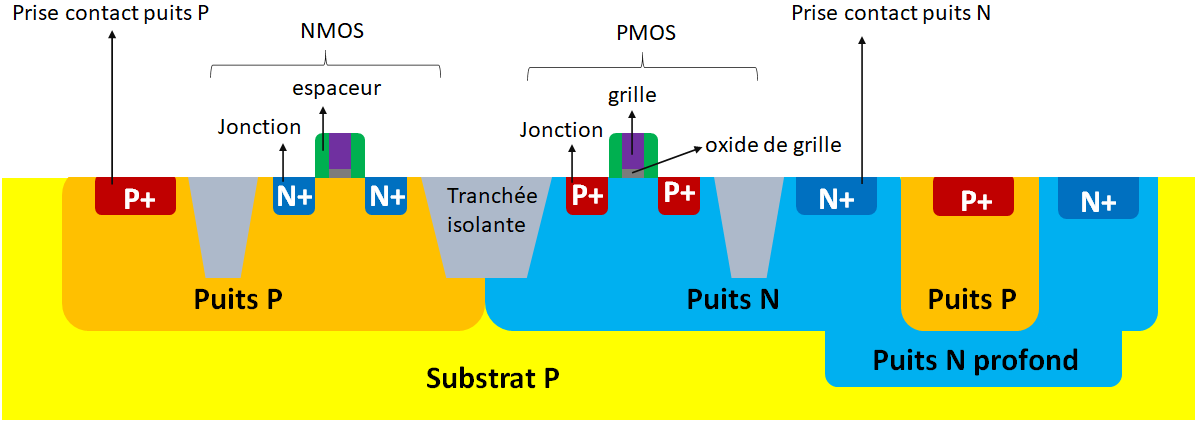

La technologie CMOS (Complementary Metal-Oxide-Semiconductor) exploite une architecture symétrique de transistors MOSFET à enrichissement, combinant des NMOS (canal N) et des PMOS (canal P) dans une configuration en push-pull. Lorsqu’un état logique est stable, l’un des transistors est bloqué tandis que l’autre est en conduction inverse, minimisant ainsi les courants de fuite statiques à l’échelle du picoampère. Cette structure bipolaire permet une consommation dynamique réduite, principalement due aux transitions de charge et de décharge des capacités parasites des grilles MOS, dont la valeur typique se situe entre 1 et 10 femtofarads. L’énergie dissipée lors du basculement logique est proportionnelle à CV²f, où C est la capacité de charge, V la tension d’alimentation et f la fréquence d’horloge. Avec des tensions d’alimentation descendant sous 1V et des fréquences atteignant plusieurs GHz, le CMOS assure un compromis optimal entre vitesse de commutation, densité d’intégration et dissipation thermique.

Comparaison NMOS vs PMOS

| Type de transistor | Canal | Conductivité | Consommation d’énergie |

|---|---|---|---|

| NMOS | Négatif | Rapide | Plus élevée |

| PMOS | Positif | Moins rapide | Plus faible |

Avantages de l’architecture CMOS

- Faible consommation d’énergie

- Haute densité d’intégration

- Fiabilité et durée de vie élevée

Limitations de la technologie CMOS

Malgré ses nombreux avantages, le CMOS présente certaines limitations :

- Effet tunnel quantique : À des échelles nanométriques, les électrons peuvent traverser l’oxyde de grille, provoquant des fuites de courant.

- Échauffement thermique : Bien que la consommation soit faible, les circuits hautement intégrés génèrent de la chaleur.

- Vitesse de commutation limitée : Pour des fréquences très élevées, la résistance des interconnexions devient un facteur limitant.

Alternatives et évolutions

Face aux limites du CMOS, plusieurs alternatives sont en cours de développement :

| Technologie | Avantages | Inconvénients |

|---|---|---|

| FinFET | Moins de fuites, meilleure performance | Fabrication plus complexe |

| Nanotubes de carbone | Très haute mobilité des électrons | Technologie encore expérimentale |

| Spintronique | Ultra faible consommation | Coût et complexité |

Conclusion

Le CMOS reste aujourd’hui la technologie dominante pour la fabrication des circuits intégrés, mais les défis liés à la miniaturisation ouvrent la voie à de nouvelles approches qui pourraient révolutionner l’industrie des semi-conducteurs.